“半导小芯”成长记:一枚芯片的设计修炼之路

你口袋里的手机能刷视频、智能手表能测心率,背后都藏着无数“半导小芯”的功劳。这些指甲盖大小的芯片,并非天生自带“超能力”,其成长始于一场微米级的精密设计修炼。今天,我们就跟随“半导小芯”的脚步,看看它从想法变为生产蓝图的全过程。

核心指引:芯片设计全流程可视化地图

1. 规格定义:输出芯片功能/功耗/成本需求清单(如智能手环传感器芯片:心率精准采集、续航一周);

2. 架构搭建:工具(Synopsys CoCentric)→ 输出模块架构图(传感器/计算/存储模块);

3. 前端设计:工具(Active-HDL/LEDA/VCS)→ 输出门级网表;

4. 后端设计:工具(Cadence Silicon Ensemble/Simens EDA Calibre)→ 输出物理版图;

5. Tape out(流片):输出GDSⅡ格式文件(晶圆厂生产图纸)。

第一步:规格定义――明确小芯“成长目标”

芯片设计如同盖摩天大楼,需先明确核心需求。“半导小芯”的第一步是敲定“人生目标”:以智能手环传感器芯片为例,工程师会定下精准采集心率、低功耗续航一周、控制成本等规则。这些要求是小芯的“成长手册”,后续所有设计均围绕其展开。

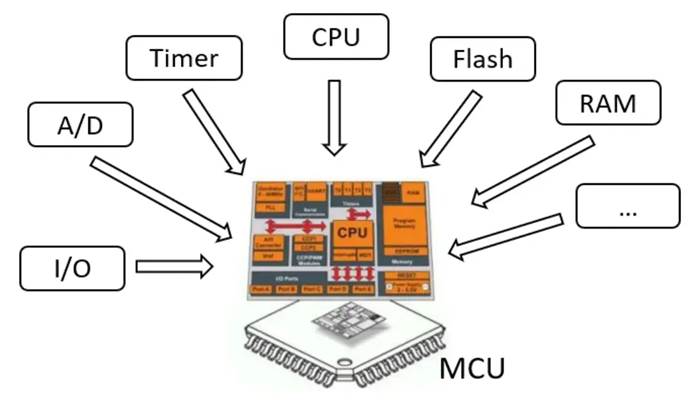

第二步:架构搭建――筑牢小芯“功能骨架”

明确目标后,架构工程师将小芯功能拆分为传感器、计算、存储等模块,规划模块协同逻辑。这一步需借助工具验证方案可行性,常用Synopsys CoCentric软件搭建模型,模拟模块配合状态(如测试计算与存储模块响应速度),及时调整布局避免后续返工。

第三步:前端设计――给小芯注入“灵魂代码”

骨架搭好后,前端工程师用Verilog HDL或VHDL硬件描述语言写代码,定义电路工作方式(如指令传感器每0.5秒采集一次数据)。Active-HDL是常用编码工具,支持代码编写与电路图可视化;代码完成后,Synopsys LEDA工具可排查逻辑漏洞。

随后通过前仿真验证功能:用Synopsys VCS或Simens EDA ModelSim模拟不同场景(如手环运动状态),确保数据采集与处理精准。功能达标后,借助Synopsys Design Compiler进行逻辑综合,按“面积<2mm²、延迟<1μs”等约束,从标准单元库挑选门电路,生成详细的门级网表。

最后完成两项关键检查:Synopsys Prime Time做静态时序分析(确保电路响应顺畅),Synopsys Formality做形式验证(保证网表与代码逻辑一致)。

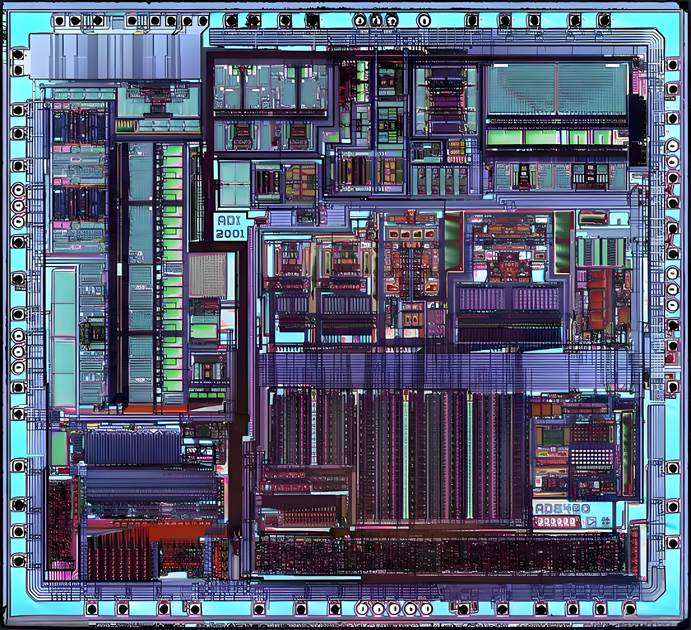

芯片设计与验证(图片来源自网络)

第四步:后端设计――打造小芯“实体身躯”

前端输出的“电路蓝图”需转化为可生产的物理版图。工程师先收集晶圆厂库文件,再用Cadence Silicon Ensemble等工具做布局规划(如将高功耗计算模块置于散热区),随后自动放置标准单元、生成时钟树(同步电路信号)。

接下来进行布线,用金属导线连接各单元与引脚,需严格遵守工艺规则减少延迟;布线完成后做后仿真,结合导线寄生参数验证时序。最终通过Simens EDA Calibre工具完成版图验证:DRC检查(避免短路)、LVS对比(防止布线错误),问题修正后输出GDSⅡ文件。

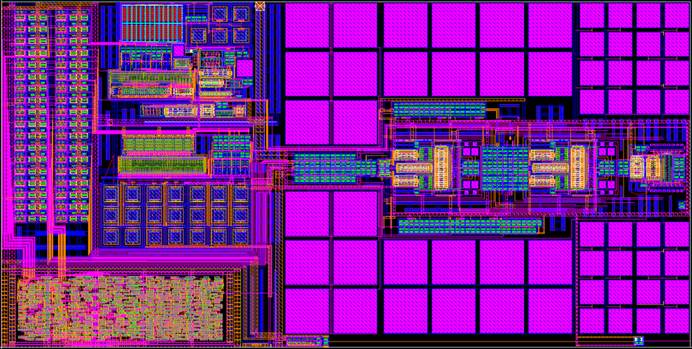

芯片版图(图片来源于网络)

芯片版图放大后细节(图片来源于网络)

终章:Tape out――小芯的“设计毕业礼”

所有验证通过后,GDSⅡ文件通过Tape out(流片)发送给晶圆厂,“半导小芯”的设计修炼正式完成,即将进入制造环节。

赋能重庆:高端芯片设计支撑“416”科创战略

芯片设计是半导体产业的核心环节,更是支撑重庆“416”科技创新战略的关键力量。重庆聚焦智能网联汽车、高端装备等重点产业集群,而高端芯片正是这些产业的“核心大脑”――智能网联汽车的自动驾驶决策、高端装备的精准控制,均离不开定制化的高端芯片设计支撑。

本土芯片设计企业与科研机构的技术突破,能为重庆相关产业提供定制化芯片解决方案,缩短供应链周期、提升产品竞争力,助力“416”科创战略落地,推动区域产业高质量发展。